デジタル信号最終段の I2S-HDMI と SPDIF/Coaxicial同軸 それぞれのケーブル構造の違いによる音質差の報告と考察です。DAC電源の種類による音傾向も加味されます。私の環境は マイルーム にあります。

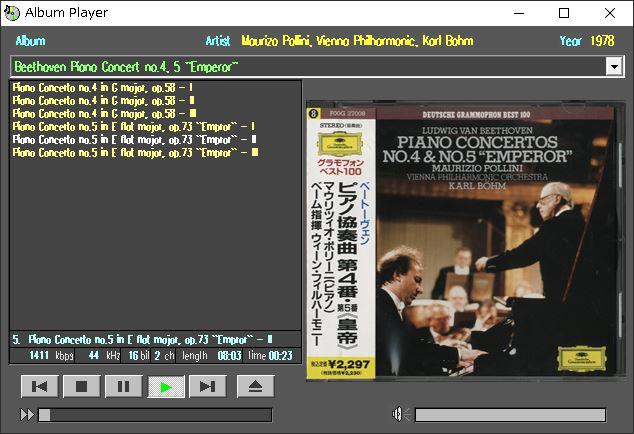

カール・ベーム指揮 ウィーン・フィルハーモニー管弦楽団 マウリツィオ・ポリーニのピアノによるベートーヴェン「ピアノ協奏曲第5番 皇帝」です。

Album Player miniの設定は最も負荷が軽くジッター低減できるようにしています。FLACのデコードやキャップレス再生のプロセスを止めており、その分CPU負荷が減ります。

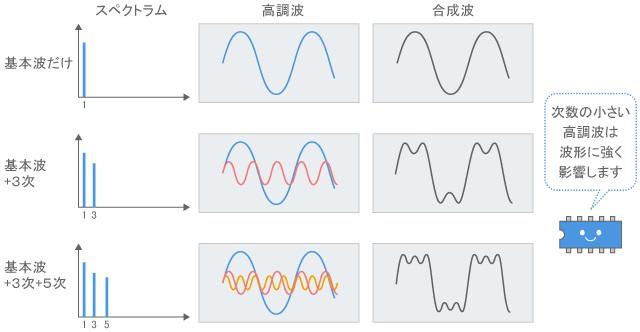

デジタルとアナログ信号の違いは矩形波と正弦波と見なすことができます。

(以下3枚の図は 電磁ノイズが発生するしくみ | ノイズ対策 基礎講座 | 村田製作所 から引用)

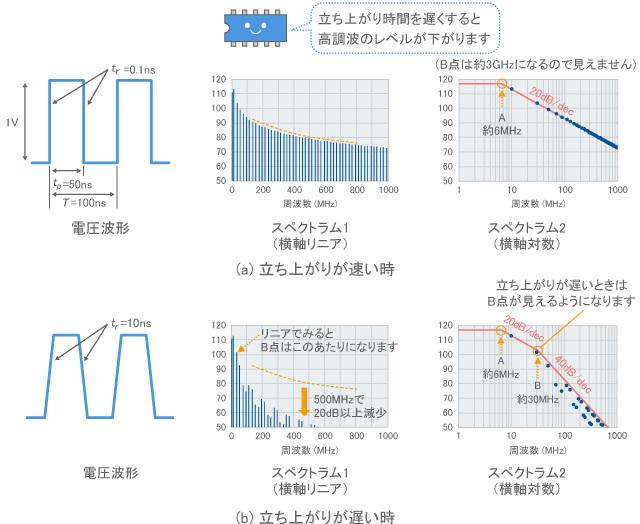

矩形波は基本波に高調波が加わったもので、理想的な矩形波は -6dB/Oct.で減衰する無限の高調波を含みます。これは電波となり電磁ノイズも発生させます。

周波数10倍となる10次高調波まできれいに伝達できると、一般的なデジタル信号としての要件を満たす台形のような波形となります。

USB DDCからの I2S-HDMI にはLVDS3.3Vで、以下のデジタル信号が別ラインで流れます。(以下ウィキペディアから引用)

・LRCLK:LR Clock(エルアールクロック)。2チャンネルステレオにおいて、音声信号のLチャネルとRチャネルを区別するための信号。WDCLK(Word Clock – ワードクロック)

・BCLK:Bit Clock(ビットクロック)。SDATAの信号のタイミングに合わせてラッチする。これによりSDATAが若干ぶれてもビット列を正確に伝送することが出来る。SCLK(Serial Clock – シリアルクロック)

・SDATA:Serial Data(シリアルデータ)。デジタル化された音声データのビット列である。

・MCLK:Master Clock(マスタークロック)。デジタル信号の動作基準となるクロック信号。ICによっては、外部からクロックを供給せずに、上記3信号と同期するようにしてMCLKの供給が必要になることがある。SYSCLK(System Clock – システムクロック)

SPDIF/Coaxicial同軸では全部混合された1つのラインだけです。簡単に言うとHDMIは同軸の4倍の高調波ノイズをDACに与えていることになります。このノイズがDACからアンプに入ると高域の量感が増えはじめ、ついには歪みとなってうるさく感じてきます。

追記:クロックは1と0が等間隔で繰り返されるきれいな矩形波ですが、データは不規則な矩形波となり高調波にうねりが生じます。データレートが上がりインパルスのようになる場合(基本波より低い帯域も含めて)全帯域にノイズを出します。

私は現在入手可能な最低速度HDMI ver1.4のケーブルを使っています。ver2.0、ver2.1と高速=高周波対応となるほどうるさく感じました。

Coaxicial同軸では長さと構造によっては高調波ノイズの減衰があり、高域の量感が減って倍音が消えるように感じました。私は2重シールド線を使っています。

DACは電源ノイズの影響も大きく、低周波スイッチングのリニア電源では低域が豊かに、高周波スイッチングのSi/GaN電源では高域が豊かになる傾向があります。I2S-HDMIとリニア電源、Coaxicial同軸とスイッチング電源の組み合わせがバランスが取れるように思います。

高調波の電磁ノイズの詳細は以下のHPをご覧ください。

電磁ノイズが発生するしくみ | ノイズ対策 基礎講座 | 村田製作所

コメント ※編集/削除は管理者のみ